## Development of a modular and fully-digital PCIe-based interface to Real-Time Digital Simulator

## Entwicklung einer modularen und voll digitalen PCIe-basierten Schnittstelle zum digitalen Echtzeit Simulator RTDS

Steffen Vogel Matriculation Number: 304957

Master Thesis

$\operatorname{at}$

RWTH Aachen University Faculty of Electrical Engineering and Information Technology Institute for Automation of Complex Power Systems Univ. Prof. Dr.-Ing. Antonello Monti

> Supervisor: Marija Stevic Dr. rer. nat. Stefan Lankes

### **Eidesstattliche Versicherung**

Ich, Steffen Vogel (Matrikelnummer 304957), versichere hiermit an Eides Statt, dass ich die vorliegende Masterarbeit mit dem Titel

Entwicklung einer modularen und voll digitalen PCIe-basierten Schnittstelle zum digitalen Echtzeit Simulator RTDS

selbstständig und ohne unzulässige fremde Hilfe erbracht habe. Ich habe keine anderen als die angegebenen Quellen und Hilfsmittel benutzt. Für den Fall, dass die Arbeit zusätzlich auf einem Datenträger eingereicht wird, erkläre ich, dass die schriftliche und die elektronische Form vollständig übereinstimmen. Die Arbeit hat in gleicher oder ähnlicher Form noch keiner Prüfungsbehörde vorgelegen.

Ort, Datum

Unterschrift

#### Belehrung

#### §156 StGB: Falsche Versicherung an Eides Statt

Wer vor einer zur Abnahme einer Versicherung an Eides Statt zuständigen Behörde eine solche Versicherung falsch abgibt oder unter Berufung auf eine solche Versicherung falsch aussagt, wird mit einer Freiheitsstrafe bis zu drei Jahren oder mit Geldstrafe bestraft.

#### §161 StGB: Fahrlässiger Falscheid; fahrlässige falsche Versicherung an Eides Statt

- (1) Wenn eine der in den §§ 154 bis 156 bezeichneten Handlungen aus Fahrlässigkeit begangen worden ist, so tritt Freiheitsstrafe bis zu einem Jahr oder Geldstrafe ein.

- (2) Straflosigkeit tritt ein, wenn der Täter die falsche Angabe rechtzeitig berichtigt. Die Vorschriften des §158 Abs. 2 und 3 gelten entsprechend.

Die vorstehende Belehrung habe ich zur Kenntnis genommen:

Ort, Datum

Unterschrift

# Kurzfassung

Diese Arbeit befasst sich mit der Entwicklung digitaler Schnittstellen zur Kopplung von Echtzeitsimulatoren. Zu diesem Zweck wurde ein flexibles Framework implementiert, welches den synchronisierten Austausch von Simulationsdaten ermöglicht. Harte Echtzeitanforderungen und die damit verbundenen Anforderungen an Kommunikationslatenzen im Mikrosekundenbereich machen eine FPGA-basierte Implementierung unumgänglich. Das VILLASfpga genannte Framework basiert auf Xilinx's aktuellen Entwicklungsumgebung und nutzt AXI4 und AXI4-Stream Busse, um bestehende IP Komponenten zu integrieren und deren Wiederverwendbarkeit zu gewährleisten. Beispiele für solche Bausteine sind Modelle, die mit Hilfe von Xilinx's Vivado System Generator for DSP (XSG) und Vivado High-level Synthesis (HLS) Werkzeugen entwickelt wurden oder auch Schnittstellen zu kommerziellen Simulatoren von RTDS oder OPAL-RT. Des Weiteren ermöglicht eine PCIe Schnittstelle den Informationsaustausch zwischen dem Field Programmable Gate Array (FPGA) und der bereits existierenden VILLASnode Software. Von speziellem Interesse ist die Kopplung des Echtzeitsimulators von RTDS mit dieser Software, da sie eine Reihe neuer Anwendungsmöglichkeiten eröffnet und die Flexibilität des Simulators steigert. Sowohl die Schnittstelle zum RTDS Simulator als auch die PCI Express (PCIe) Schnittstelle zwischen FPGA und Linux-Rechner wurden im Hinblick auf ihre Echtzeitfähigkeit ausführlich getestet. Einfache Modelle auf dem FPGA und Linux-Rechner wurden verwendet, um die Erweiterbarkeit und Flexibilität des Frameworks zu demonstrieren.

Stichwörter: Echtzeit, Co-Simulation, RTDS, GTFPGA, PCIe, Schnittstelle

## Abstract

This thesis focuses on the development of digital interfaces for the interconnection of Digital Real-Time Simulation (DRTS). For this purpose, a flexible framework has been implemented to facilitate the synchronized exchange of simulation data. Hard real-time requirements and low communication latencies necessitate a FPGA-based implementation. The VILLAS fpqa named framework uses Xilinx' latest FPGAs and design tools. It is built around industry standard AXI4 and AXI4-Stream interfaces to warrant reusability and integration of existing Intellectual Property (IP) components. Examples for such components are models implemented with Xilinx's XSG and HLS tools or interfaces to commercial DRTSs from RTDS or OPAL-RT. Furthermore, a PCIe interface is used to integrate the FPGA framework with the existing VILLAS node software. Coupling the DRTS from RTDS with this software is of special interest as it opens a variety of new applications and increases the overall flexibility of the simulator. Both the PCIe and Real-time Digital Simulator (RTDS) interfaces have been evaluated in regard to their real-time performance. Simple models on the FPGA and the Linux machine have been used to demonstrate the extensibility and performance of the framework.

Keywords: Real-time, Co-Simulation, RTDS, GTFPGA, PCIe, Interface

# Contents

| 1 | Intro             | duction                                                                                                                                              | 1 |  |  |  |  |  |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

|   | 1.1               | Motivation                                                                                                                                           | 1 |  |  |  |  |  |

|   | 1.2               | Objective                                                                                                                                            | 2 |  |  |  |  |  |

|   |                   | 1.2.1 Applications                                                                                                                                   | 3 |  |  |  |  |  |

|   | 1.3               | Related work                                                                                                                                         | 4 |  |  |  |  |  |

|   | 1.4               | Structure                                                                                                                                            | 5 |  |  |  |  |  |

| 2 | The               | pretical background                                                                                                                                  | 7 |  |  |  |  |  |

|   | 2.1               | Real-time Simulation                                                                                                                                 | 7 |  |  |  |  |  |

|   | 2.2               | Co-operative Simulation                                                                                                                              | 7 |  |  |  |  |  |

|   | 2.3               | Soft & Hard Real-time Computing                                                                                                                      | 9 |  |  |  |  |  |

|   | 2.4               |                                                                                                                                                      | 9 |  |  |  |  |  |

|   | 2.5               | Člock Hierarchy                                                                                                                                      | 0 |  |  |  |  |  |

|   | 2.6               | Scheduling                                                                                                                                           |   |  |  |  |  |  |

|   | 2.7               | Computer Architecture                                                                                                                                |   |  |  |  |  |  |

|   |                   | 2.7.1 Direct Memory Access (DMA) & Programmed IO (PIO) 14                                                                                            |   |  |  |  |  |  |

|   |                   | 2.7.2 Polling & Interrupts 14                                                                                                                        |   |  |  |  |  |  |

| 3 | ٥٠٠٠              | itecture 1                                                                                                                                           | 7 |  |  |  |  |  |

| 3 |                   |                                                                                                                                                      | - |  |  |  |  |  |

|   | $3.1 \\ 3.2$      |                                                                                                                                                      | - |  |  |  |  |  |

|   | 0.2               |                                                                                                                                                      | - |  |  |  |  |  |

|   |                   |                                                                                                                                                      |   |  |  |  |  |  |

|   |                   |                                                                                                                                                      |   |  |  |  |  |  |

|   |                   |                                                                                                                                                      |   |  |  |  |  |  |

|   | <u></u>           | 3.2.4 Models                                                                                                                                         |   |  |  |  |  |  |

|   | 3.3               | VILLASnode                                                                                                                                           |   |  |  |  |  |  |

|   | 3.4               | Host Machine $\dots \dots \dots$                     | - |  |  |  |  |  |

|   |                   | 3.4.1 Userspace IO (UIO) $\ldots$ 22                                                                                                                 |   |  |  |  |  |  |

|   | 95                | 3.4.2 Virtual Function IO (VFIO) $\dots \dots \dots$ |   |  |  |  |  |  |

|   | 3.5               | Real-time Digital Simulator (RTDS) 29                                                                                                                |   |  |  |  |  |  |

|   |                   | 3.5.1 Giga Tranceiver Network card (GTNET)                                                                                                           |   |  |  |  |  |  |

|   |                   | 3.5.2 Giga Tranceiver Field Programmable Gate Array (GTFPGA) 3                                                                                       |   |  |  |  |  |  |

|   |                   | 3.5.3 Giga Tranceiver Synchronization card (GTSYNC) 34                                                                                               | 4 |  |  |  |  |  |

| 4 | Implementation 37 |                                                                                                                                                      |   |  |  |  |  |  |

|   | 4.1               | FPGA Evaluation Board                                                                                                                                | 7 |  |  |  |  |  |

|   |                   | 4.1.1 Small Form-factor Pluggable (SFP) Fiber Module 38                                                                                              | 8 |  |  |  |  |  |

|                | 4.0           | 4.1.2 PCI Express (PCIe) Interface                         |              |  |  |  |  |  |

|----------------|---------------|------------------------------------------------------------|--------------|--|--|--|--|--|

|                | 4.2           | IP cores                                                   |              |  |  |  |  |  |

|                |               | 4.2.1 Data-movers                                          | . 41         |  |  |  |  |  |

|                |               | 4.2.2 FPGA Models                                          |              |  |  |  |  |  |

|                |               | 4.2.3 RTDS Interface                                       |              |  |  |  |  |  |

|                |               | 4.2.4Interrupt Controller                                  |              |  |  |  |  |  |

|                | 4.3           | 7                                                          |              |  |  |  |  |  |

|                | 4.3<br>4.4    | Vivado IP Integrator (IPI)                                 |              |  |  |  |  |  |

|                | 4.4           | 4.4.1 Linux Real-time optimizations                        |              |  |  |  |  |  |

|                |               | 4.4.1       Linux Rear-time optimizations                  | . 57<br>. 60 |  |  |  |  |  |

|                | 4.5           | Synchronization                                            |              |  |  |  |  |  |

|                | 4.6           | Design Flow                                                |              |  |  |  |  |  |

|                | 4.0           | 4.6.1 Software                                             |              |  |  |  |  |  |

|                |               | 4.0.1 Software                                             | . Ut         |  |  |  |  |  |

| 5              | Resi          |                                                            | 65           |  |  |  |  |  |

|                | 5.1           | Test System                                                |              |  |  |  |  |  |

|                | 5.2           | Interface                                                  |              |  |  |  |  |  |

|                |               | 5.2.1 PCIe Interface                                       |              |  |  |  |  |  |

|                | 5 0           | 5.2.2 RTDS Interface                                       |              |  |  |  |  |  |

|                | 5.3           | Applications                                               |              |  |  |  |  |  |

|                |               | 5.3.1 Simple Circuit                                       |              |  |  |  |  |  |

|                |               | 5.3.2 Hybrid DP-EMT simulation                             | . 73         |  |  |  |  |  |

| 6              | Conclusion 81 |                                                            |              |  |  |  |  |  |

|                | 6.1           | Future work                                                | . 81         |  |  |  |  |  |

| I              | Ар            | pendix                                                     | 85           |  |  |  |  |  |

| Α              | Cod           | e examples                                                 | 87           |  |  |  |  |  |

| ~              |               | <i>VILLASnode</i> Configuration File for <i>VILLASfpga</i> |              |  |  |  |  |  |

|                | A.2           | XML: Accelerator Map of hls_multiply                       |              |  |  |  |  |  |

|                | A.3           | VHDL: hdl_multiply                                         |              |  |  |  |  |  |

|                | A.4           | HLS: hls_dft                                               |              |  |  |  |  |  |

|                |               | Linux configuration                                        |              |  |  |  |  |  |

| В              | List          | of Acronyms                                                | 97           |  |  |  |  |  |

| Lis            | st of         | Figures                                                    | 103          |  |  |  |  |  |

| List of Tables |               |                                                            |              |  |  |  |  |  |

|                |               | Listings                                                   | 107          |  |  |  |  |  |

Contents

## Bibliography

109

# **1** Introduction

#### 1.1 Motivation

This master thesis introduces a FPGA-based framework for distributed co-simulation of power systems. Advances in microprocessor technology and programmable logic devices like FPGAs and specialized Digital Signal Processors (DSPs) are key enablers of digital real-time simulation. Increasing performance, programability and competitive costs of such devices are the main factors for the heterogenous range of products which are available for real-time simulation today. At the same time, interdisciplinary studies of complex systems necessitate the integration of multiple platforms. Examples are multi-physics simulations of thermal and electric systems or the simulation of mechanical torques which can be found in wind turbines or electric vehicles. As the main motivation behind real-time simulation is testing of real devices, custom requirements lead researchers to design their own specialized Power-Hardware-in-the-Loop (PHIL) setups and experiments which need to be integrated into the simulation environment [4].

But not only the simulator hardware is becoming more heterogenous and diverse. Hybrid simulations combine multi-domain simulation approaches, such as co-simulation of Electro-magnetic transient (EMT)-based solvers with solvers based on Dynamic Phasors (DPs). In this case the interface is in charge of handling the conversion between these two domains.

The ordinary approach for coupling real-time simulation equipment is using analog signals. However, this method has a couple of disadvantages: Analog signals are inherently susceptible to externally induced noise which degrades signal quality and thereby limits the maximum length of the link. In addition, this noise limits analogdigital converters in their resolution. Likewise the operational voltage ranges of the converters are limited. Last but not least, every single signal requires a dedicated cabling which gets cumbersome in cases where a large amount of signals or parameters have to be exchanged. An interface might not always be used for the interface of 3-phase busses whose ranges are known in advance. Sometimes transfer functions or other complex parameters have to be exchanged. In case the parameters may vary of a wide range or their values are unknown, analog signals can not cover them in their full precision.

Power system simulation mainly requires solving of large and sparse matrix equations and has therefore been a compute-bound problem. Gordon Moore predicted the tremendous growth of computation power for the last decades. Lately, Moore's law lost its validity due to processors hitting the so called *power-wall*. The increas-

#### 1 Introduction

ing integration density and higher clock speeds are demanding more power which as a result has to be dissipated as heat. However, the amount of energy which can be dissipated is limited by physics. This restriction has been a catalyst for the development of multi-core processors, distributed systems and specialized accelerators. As a consequence, power system simulation has become a communication- instead of a compute-bound problem. Especially real-time simulation is susceptible to this bottleneck as hard deadlines must be met.

Finally, competition between vendors is an obstacle for integration. There is currently no standard for real-time co-simulation. This motivated the design of a vendor-neutral hub for real-time co-simulation. Such a central hub could act a gateway between a arbitrary number of simulation nodes (simulators, Hardware-in-the-Loop (HIL) interfaces, monitoring and control devices or software). In future, this hopefully reliefs researchers from the burden of interface design and allow them to focus on their research assignment.

Point-to-point interfaces are usually sufficient for simple setups with not more than two nodes (simulators or HIL devices). But as soon as more nodes are involved the number of possible point-to-point interfaces scales quadratic. A central interconnect can alleviate this issue by providing a common interconnect for all interfaces. Adding support for a simulator becomes easy as only a single new interface must be implemented.

### 1.2 Objective

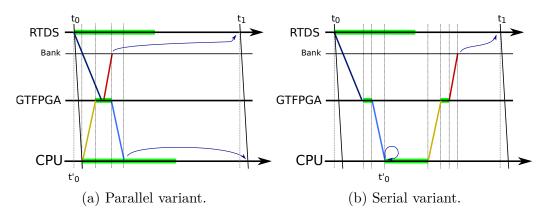

First ideas for this thesis arose from the demand of an interface between RTDS's DRTS and a Linux-based x86-machine. A requirement for such an interface has been the ability to synchronize exchanged signals with the time step of the RTDS simulator. Existing communication protocols supported by RTDS do not offer this feature with the exception of a FPGA-based extension card called GTFPGA. Interfacing a commercial simulator to a generic Personal Computer (PC) and FPGA significantly simplifies development of generic interfaces and thereby opens a new range of possibilities.

Previous work implemented a flexible *soft* real-time co-simulation hub on a Linux machine with similar goals. We named this software  $VILLASnode^1$ . Following this scheme, the new FPGA-based framework for *hard* real-time co-simulation is called VILLASfpga. Based on the GTFPGA card, it realizes a flexible interconnect for a variety of components involved in real-time simulation like DRTSs, FPGA-models or custom HIL interfaces. This framework lays out the foundation for future projects, emphasis on a well-thought-out design is therefore important. As motivated in the previous section, it should support the extension with new interfaces like real-time industrial ethernet (e.g. EtherCAT) or custom Aurora based communication links like OPAL-RT Opal Remote IO Network (ORION) [6]. The interface to RTDS is just one of many possible extensions and is presented here as an example.

<sup>&</sup>lt;sup>1</sup>Previous publications also named it Simulator-to-Simulator Server, Sim2SimServer or S2SS.

Models on the FPGA should be implemented with XSG or HLS to provide unexperienced FPGA users a simple design entry method. An integration with the existing *VILLASnode* software simplifies the usage by combining both the *VIL-LASnode* and *VILLASfpga* configuration in a single file. At the same time, all the existing interfaces which are supported by *VILLASnode* can be connected to the new FPGA-based interconnect. *VILLASnode* provides an easy-to-use C Application Programming Interface (API) for controlling and data exchange with the FPGA framework. To leverage the performance of a FPGA implementation in conjunction with the flexibility of *VILLASnode* a bridge between the FPGA and the Central Processing Unit (CPU) is required. PCIe is the only user accessible, low-latency, high-bandwidth interface in modern x86-based machines. It has to be employed for synchronization and data exchange between the FPGA and CPU.

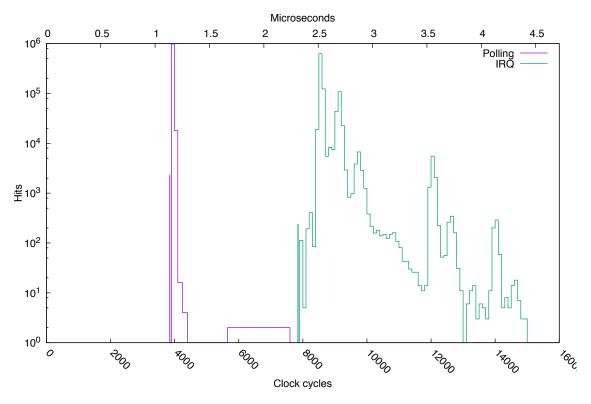

There is a number of industry standards protocols for Supervisory Control and Data Acquisition (SCADA) and substation automation tasks. The most prominent one is IEC 61850 which specifies Generic Object Oriented Substation Events (IEC 61850-8-1) (GOOSE) and Sampled Values (IEC 61850-9-2) (SV). These standards often define data structures which are far to complex for the task of real-time cosimulation. Most power system simulators have built-in support for those protocols to test existing automation equipment and understand the influence of the protocols in the system<sup>2</sup>. Due to the lack of alternatives, previous digital co-simulations often used those protocols. However, none of them is actually designed for this purpose and none of them has the notion of a simulation time step. There is no standardized protocol which supports the synchronization with the accuracy of a simulation time step in the range of 10 to 50 µs. In real-time co-simulation (not co-simulation of communication protocols), the interface and the underlying protocols are not the subject of the experiment. In fact, they are just the tool to enable them. Ideally, their presence ideally would not have an impact onto the results of the simulation. However, due to inevitable communication latencies this is not the case. Special interface algorithms and decoupling methods must be employed.

In some applications like thermal / electric co-simulation, the communication latency can be neglected as the thermal subsystem is running at much lower rate as the electric subsystem. In this thesis, we focus on the implementation of a singlerate interface as it has the most strict requirements. By demonstrating that these tight timing requirements can be met, we implicitly show that the same interface can also be used for less stringent demands.

#### 1.2.1 Applications

In addition to the original goal, this framework envisioned to be used for the following use cases:

**Real-time co-operative simulation** The model is separated into two subsystems of which both are simulated in EMT-domain. One subsystem is simulated in

<sup>&</sup>lt;sup>2</sup>E.g. for OPAL-RT: http://www.opal-rt.com/communication-protocols.

#### 1 Introduction

the real-time simulator while the other is simulated in real time by the Linux machine. The interface delay is compensated based on a Bergeron traveling-wave model of a transmission line.

- **Hybrid simulation** The model is separated into two subsystems of which one is simulated in DP-domain. This enables simulation of large-scale subsystems in the phasor domain on the Linux machine or a dedicated High-performance Computing (HPC) cluster. Regions of interest can still be simulated in high resolution EMT-domain on the real-time simulator with a much smaller time step than the phasor subsystem.

- **Geographically-distributed simulation** Co-simulation over large geographical distances will be affected by significant communication latencies. These latencies have to be predicted and compensated by using interface algorithms that can be based on Discrete Fourier Transform (DFT) and wavelet transforms. Especially on public networks like the internet these latencies are hard to predict. A central hub per laboratory can act as a gateway which implements those interface algorithms and manages data exchange.

- **User interaction & Monitoring** Interaction with real-time simulations is usually done via vendor-specific tools like RTDS's RTDS Simulator Software (RSCAD) or OPAL-RT's RT-LAB. Most of them already provide APIs to interact with the simulator. Previous work has shown a web-interface for *VILLASnode* which allows users to monitor and control the simulation using standard web-browsers.

- **Big data analytics** The presented framework offers the ability to record and replay signals continuously for each and every time step of the simulation in a customized and flexible manner. The collected results can be stored in Time-series Database (TSDB) for subsequent offline analysis. Big data analytic methods could be applied to study the vast amount of data. Existing record and replay features only offer a limited sampling rate and a limited number of signals.

### 1.3 Related work

During the work on this thesis, ACS and OPAL-RT demonstrated the first fullydigital interface between a RTDS rack and an OPAL-RT eMegaSim simulator [16]. For the first time, a synchronized and fully-digital co-simulation with only a single time step latency between both real-time simulators has been possible.

The OPAL-RTDS interface as well as the interface which is presented in this thesis are based on the *GTFPGA* block which has been block specifically developed in a collaboration between RTDS Technologies and Florida State University's Center for Advanced Power Systems (CAPS) in 2009 [22] [24]. Since then, it was used regularly used by CAPS for various research projects. Berger used it to implement a RTDSto-Aurora bridge for Controller-Hardware-in-the-Loop (CHIL) testing [5]. Stanovich et al. implemented a Multi-agent testbed using a RTDS-to-Ethernet gateway [25]. Rentachintala presents a co-simulation interface between RTDS and OPAL-RT using a 11 bit parallel bus [21].

A combination of the GTFPGA block with PCIe interfaces was first mentioned by Stanovich et al. in [26] and by Hu et al. in [10] in 2013. Unfortunately, both publications lack details about their PCIe implementation.

RTDS supports distributed simulation across multiple RTDS racks by using a custom Inter Rack Communication switch (IRC) switch which is described in chapter 3.5. However their internal communication protocol is undocumented. The only possibility to get access to their simulator backplane is by using the GTFPGA block.

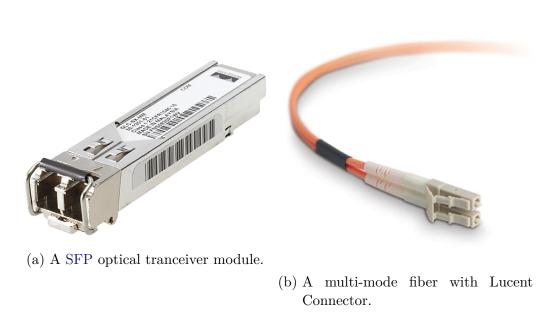

OPAL-RT itself offers Aurora-based communication interfaces using SFP fiber optics for their simulators<sup>3</sup>. Aurora (8B10B) is a data-link layer protocol developed by Xilinx for high speed communication. The primary use-case of the interface is for FPGA-to-FPGA communication or Modular Multi-level Converters (MMCs) applications. When carefully designed it could also be used to connect multiple RT-LAB nodes. However, the designated method for multi-target co-simulation is the RT-LAB software [17]. RT-LAB supports FireWire, Infiniband, Shared Memory (PCIe Scalable Coherent Interface (SCI)) as underlying communication protocols.

In 2006, OPAL-RT introduced Orchestra, a software communications framework for real-time data exchange between RT-LAB Simulink-based models and external software or hardware components [7]. Orchestra is built on top of the RT-LAB software and therefore uses the same communication channels as RT-LAB. A custom Orchestra API allows the integration of various software-based simulation tools like Matlab/Simulink, Dymola or MATRIXx. Orchestra is real-time capable and was inspired by the publish / subscribe concept of High Level Architecture (HLA) and uses Extensible Markup Language (XML) for Distributed Data Structures (DDS). A first application of this framework was presented in [18]. Paquin et al. present a real-time co-simulation of an All-Electric Ship (AES) which is performed by a total of three RT-LAB targets. Communication is done via Remote Memory Access (RMA) over a Dolphin SCI interconnect.

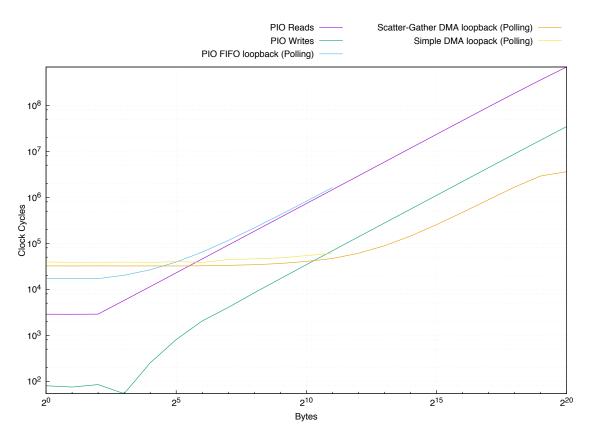

Finally, Flajslik et al. present techniques to reduce the PCIe communication latency for low-latency applications [9]. Using a FPGA prototyping board, they present PIO and polling techniques which enables a direct data-transfer between the FPGA and CPU without accessing the main memory of the system.

### 1.4 Structure

This introduction is followed by a brief introduction into the basics of real-time simulation. The theory of co-operative simulation and the required synchronization and communications schemes are covered in detail. Basic topics of modern computer

<sup>&</sup>lt;sup>3</sup>http://www.opal-rt.com/aurora

architectures like interrupts and DMA are introduced as this work builds a bridge between between computer and power system engineering.

The next chapter 3 covers the architecture of the co-simulation framework. It starts off with the concept of the *VILLASnode* and continues by showing how this concept has influenced the architecture of the FPGA-based hub. The architecture describes main building blocks and their relationship. Different methods for data transfer and synchronization between the FPGA and the host CPU are compared.

The implementation chapter 4 contains detailed descriptions of the aforementioned components. It shows the design flow used for implementation and depicts ways to extend the framework with new components or models.

Functionality and performance of the framework is evaluated in chapter 5. Counterbased models are presented to calculate time step-accurate round-trip time measurements. Simple electrical models are used to showcase real-time co-simulations and hybrids simulations between the Linux host and RTDS.

Finally the last chapter 6 summarizes the result, shows some example applications and gives an outlook for possible future work.

## 2 Theoretical background

### 2.1 Real-time Simulation

A simulation is a representation of the operation or features of a system through the use or operation of another [27]. This thesis focuses on the digital real-time simulation of electric power systems. Models are executed on specialized real-time capable simulators or optimized computer systems. The most common approach for the simulation of EMT-based models are fixed time step solvers. They approximate the state of a time-continous model at discrete points in time whereas the state is solely depending on the results of previous calculations and current inputs. The period between two consecutive computations is called *time step*.

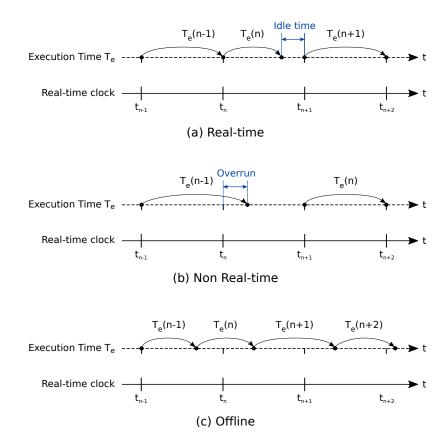

Real-time simulation refers to a model of a physical system that is executed at the same rate as the actual *wall clock* time. A fixed time step solver has the advantage that it can be executed in real time as long as the computation time does not exceed the time step. Case (a) of figure 2.1 shows a fixed time step simulation which meets this criterion. In case (b) the deadline for time step n is missed out which causes an overrun and the next step to be skipped. In comparison, the last case (c) displays an offline simulation. Time steps are executed immediately one after the other without idle delay in between.

Both Faruque [8] and Belanger [3] summarize the current state of the art in realtime simulation electric power systems.

### 2.2 Co-operative Simulation

Co-operative simulation, or short co-simulation, describes the distributed simulation of multiple subsystems which form a coupled system. Every subsystem is modelled independently without detailed knowledge about details of the remaining system. Usually, systems are decoupled across spatial boundaries like a transmission line and only exchange a limited number of interface quantities. By limiting the amount of exchanged information, every subsystem can be solved with a dedicated method and / or timestep. In the context of power system simulation, a nodal admittance matrix has be decomposed into several smaller problems.

There are several motives that make co-simulation indispensable and helpful that at the same time may come with challenges:

• Different simulation tools often have to be integrated into a single simulation environment. Legacy models are sometimes hard to port to a new simulation

#### 2 Theoretical background

Figure 2.1: Fixed time step simulation [8].

tool or certain models require specific libraries which are only available in a specific tool.

- Hybrid simulations may consist of EMT and DP-based subsystems. This requires decoupling and conversion between the time and time-frequency domain at subsystem boundary.

- Multi-physics simulations are an example where multiple time steps are used throughout the model as well as diverse simulation models. Thermal models are executed with time steps which are magnitudes larger than for electrical models. Multi-rate setups must be synchronized properly at the interface.

## 2.3 Soft & Hard Real-time Computing

Real-time computing describes hardware or software systems which are subject to a real-time constraint. This constraint is expressed in form of a deadline to which the system must complete certain computations or react to an event. For soft real-time systems, missing a deadline is acceptable but will cause in degradation of system performance. Examples are multimedia applications like video decoders or telephony. Hard real-time systems in contrast have to be designed in a way that deadlines are always met. Overruns are unacceptable and can only be caused by errors during system design. This restricts an engineer in the selection of algorithms. The amount of computation time for a hard real-time capable algorithms must be known in advance. This can be hard or even impossible to determine for iterative solvers which are therefore rarely encountered in real-time simulation.

## 2.4 Synchronization

Synchronization is the coordination of events in a distributed system in such a way that they coincidence in time. For most setups, synchronization information is signalled over the same link as data, and therefore equally affected by communication latency. This latency must be precisely estimated and compensated to guarantee a temporal coincidence of the synchronized events in both simulators. Network time protocols like Network Time Protocol (NTP), Precision Time Protocol (IEEE 1588) (PTP) or Inter Range Instrumentation Group Timecode B (IRIG-B) solve this problem by implementing algorithms like Christian's or Best Master Clock (BMC) [2].

The most commonly synchronized event between simulators are:

- 1. The start or end of a simulation case.

- 2. The beginning of a new time step.

- 3. The update or sampling of hardware Input / Outputs (IOs).

4. The completion of data exchange with other simulators.

A coordinated simulation start, ensures that results of the simulation are deterministic between runs and realistically represent a real world scenario. Only a synchronized start allows a transient response to be analysed. In AC systems, voltage and current sources generate their output in relation to a global reference phase per simulator. To couple certain active networks, the reference phases of involved simulators have to by aligned. This is usually guaranteed by starting both simulations at the same time.

The synchronization of time steps is necessary to avoid a shift between of simulator clocks. Without that, the time steps would drift apart after some time and the communication phases of both simulators would not be aligned. Furthermore, it would result in imprecise simulation results as the time step which is expected and used for the calculations does not match the real elapsed time.

The main motivation for real-time simulation is the ability to control and test real hardware. HIL experiments which are interfaced to multiple simulators require that all simulators sample their inputs at the same point in time. Sampling and the update of outputs is usually done periodically with the time step. As a result, those events are occurring relative to the time step event. In case no real hardware is attached to the simulators, the simulation actually can be simulated offline. In an offline simulation only the logical order of time steps must be observed.

In a local environment, simple optical Pulse per Second (PPS) signals or Digital IO (DIO) pins of the master simulator can be used to distribute the synchronization information. These signals are only affected by a very small latency which is usually far below 1 µs and jitter free.

However, if simulators are connected via an unreliable link like the internet, the communication latency is also affected by jitter which makes it hard to reliably estimate the latency. Under such circumstances, common time references like atomic clocks (Temps Atomique International (TAI)) or satellite navigation systems like Global Positioning System (GPS) or Globalnaja Nawigazionnaja Sputnikowaja Sistema (GLONASS) can be used as a synchronization source. They provide a highly accurate and stable clock as well as a reference to absolute global time.

### 2.5 Clock Hierarchy

Apart from simulation-related clocks, like time steps, there are typically other clocks involved in a distributed simulation as well. Processors, busses, memories, communication interfaces require their own dedicated clocking. The clock sources for those components are mostly fixed by the architecture of the simulator. As listed in table 2.1, only some of them are synchronized across the entire distributed system and others, like for simulator processors and interfaces, are not. This is due to the high clock speeds (> 100 MHz) and architectural limitations.

| Clock                | Frequency                             | Synchronized? |

|----------------------|---------------------------------------|---------------|

| Host CPU             | $3\mathrm{GHz}$ to $4\mathrm{GHz}$    | no            |

| FPGA models          | $200\mathrm{MHz}$                     | no            |

| PCIe bus             | $125\mathrm{MHz}$                     | no            |

| AXI busses           | $100\mathrm{MHz}$                     | no            |

| Simulation time step | $20\mathrm{kHz}$ to $100\mathrm{kHz}$ | yes           |

| AC Power System      | $50\mathrm{Hz}$ and $60\mathrm{Hz}$   | yes           |

Table 2.1: Clocks involved in heterogenous co-simulation.

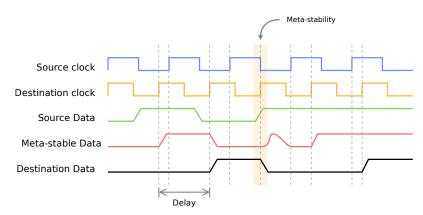

In a co-simulation, data needs to pass through several of those clocks. Whenever two clocks are asynchronous, this boundary is referred to as a Clock domain crossing (CDC). CDCs require special attention by the design engineer as they can cause meta-stability as shown in figure 2.2. A signal which is synchronous to a clock will always have a stable value at the rising edge of its clock. However, in a CDC the signal is captured by a flip flop which is synchronous to a different clock. If the rising edge of this destination clock happens to coincidence with the transition of the data signal, the resulting state of the destination flip flop is undefined and therefore meta-stable.

This problem must be resolved by synchronization circuits like a n-stage multi flop synchronizer shown in figure 2.3. By chaining multiple capture flip-flops which are clocked by the destination clock the probability for a metastable signal can be reduced. The n-stage flop synchronizer adds n cycles latency to the signal. However, if compared to the the simulation time step, this is negligible.

Figure 2.2: A meta-stable signal.

Figure 2.3: A n-stage Flop Synchronizer to mitigate meta-stability.

## 2.6 Scheduling

During a co-simulation, all involved parties periodically exchange interface quantities and compute their system solution for the next time step. The temporal order in which this is done can be altered for improving certain aspects of the interface.

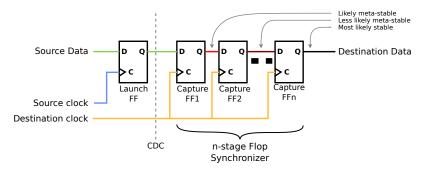

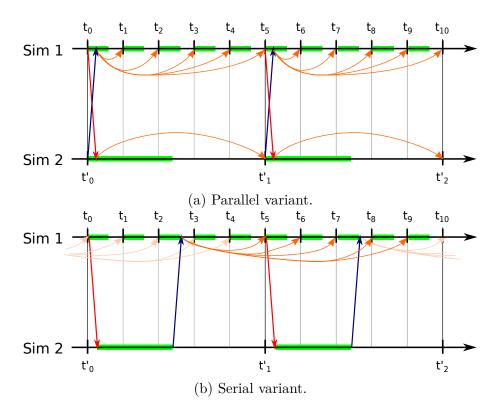

The simplest mode is shown in figure 2.4a, all simulators start their time step cycle with the exchange of interface quantities while at the same time starting to compute the solution for the next step. In this concurrent or parallel approach all exchanged quantities represent the state of the previous time step as the quantities of the current time step are yet to be calculated. This results in an inevitable communication latency of at least one time step between all simulators. This latency must be compensated by interface algorithms to guarantee system stability and simulation fidelity. For a single time step latency (typically 50 µs) transmission line models based on the travelling wave theory can be used.

Alternatively, a serial pattern can be used which is shown in figure 2.4b. Here the computation phase of two simulators has been serialized. This eliminates the single time step latency at the cost of half the available computation time per simulator and it is in contrast with main motivation behind distributed simulation concept. In contrast to the parallel exchange, the number of simulators which can participate in the serial pattern is limited by the amount of computation and latencies as they will sum up and may cause the deadline to be missed.

In a multi-rate simulation simulators run with different time step periods. The ratio between the rates still must be an integral value. A typical application is the co-simulation of a thermal - electrical systems where the thermal system runs with a much bigger time step. Figure 2.5 shows the communication pattern of a multi-rate co-simulation. Similar to the first two examples, serial and parallel patterns exists.

### 2.7 Computer Architecture

Modern computer systems are becoming more and more distributed. This applies for distributed clusters which can be found in HPC as well as for single worksta-

Figure 2.4: Co-simulation communication patterns.

Figure 2.5: Multi-rate communication patterns.

tions. These systems consist of multiple processors, a variety of peripherals like memory, network cards and disk controllers. Lately, co-processors like specialized Graphic Processing Units (GPUs), Intel's Xeon Phi or FPGA-based accelerators are supporting this trend.

When mapping simulations onto such architectures, especially real-time simulations, a closer look to synchronization and data transfer between the involved components is required.

#### 2.7.1 Direct Memory Access (DMA) & Programmed IO (PIO)

With PIO and also called Memory-mapped IO (MMIO) the CPU issues single read and write transfers for each data word. This can be done by mapping the device memory into the physically addressable memory of the CPU. For PCIe devices this mapping is configured by changing the so called PCIe Base Address Registers (BARs). The CPU can only read and write word by word which limits has the disadvantage that the CPU is kept contiguously busy similarly to polling which is described in the next subsection.

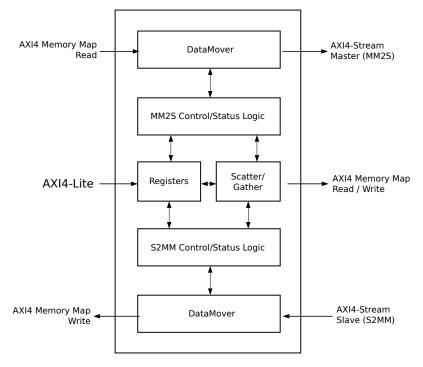

As a consequence, DMA has been invented to avoid this. As of today, most peripherals have their own DMA controllers on-board. DMA is a technique which offloads the data transfer task to a dedicated controller. The CPU instructs the DMA controller to perform a data transfer by writing to its device registers using the previously described PIO. After initiating the transfer, the CPU can directly continue with other tasks until the completion of the transfer is signalled to the CPU by one of the two previously described mechanisms.

Simple DMA controllers only support a single outstanding transfer. Once a data transfer has been configured and started, the CPU must wait for completion before the subsequent transfer can be configured. More sophisticated DMA controllers support Scatter-Gather (SG) operations. They can increase the performance of many small transfers and facilitate transfers and configuration at the same time. SG extends the simple DMA controller by adding support for multiple outstanding operations. A dedicated memory region is shared by the CPU and DMA controller to keep a queue of outstanding and completed of transfers. This queue contains *buffer descriptors* which can be seen as little work packages. Every buffer descriptor contains a source and destination address and the length of the transfer in bytes.

#### 2.7.2 Polling & Interrupts

Since the early age of microprocessors, interrupts are the standard method to synchronize peripheral devices with the main processor. Common examples are Network Interface Controllerss (NICs) which notify the CPU about new incoming data or input devices like mice and keyboards. Interrupts are triggered by asserting a special interrupt pin of the processor. This causes the CPU to pause its current task by branching into an interrupt sub routine. Because the interrupt line is shared between all peripherals the Interrupt Service Routine (ISR) has to determine which of those devices caused the interrupt. It then dispatches the interrupt service request to a device-specific handler which is part of the Operating System (OS) driver. The handler then has to react to the interrupt condition and initiate further actions.

Linux introduced a concept called *soft interrupts* which can postpone the execution of device-specific interrupt handlers to a later stage. The hardware ISR only acknowledges the interrupt and schedules a *tasklet* to handle the data intensive tasks. This mechanism has the advantage that it increases the number of interrupts which can be handled.

Often it is needless to interrupt the CPU for every event which occurred on a device. A good example are devices which generate a high amount of interrupts like network cards. The arrival of a network packet is usually worthy to trigger an interrupt. However, under high loads this would interrupt the CPU quite often and hence limit the system performance. A concept called *IRQ coalescing* reduces the load by delaying the interrupt until a certain amount of events occurred. The benefit of this technique heavily depends on the requirements of the application. In real-time applications coalescing is usually undesired because it artificially increases the latency. Yet it can be used to increase the throughput of bandwidth intense network applications.

The alternative to interrupts is *polling*. In contrast to interrupts, it does not require special hardware like interrupt lines or controllers. Polling detects events by repeatedly reading status registers of the memory of the device. This periodic reading occupies the CPU and is therefore often avoided because no other tasks can be executed while waiting for a new event. However, it can lead to a reduction of interrupt latency because there is no overhead caused by the execution of interrupt handlers.

# **3** Architecture

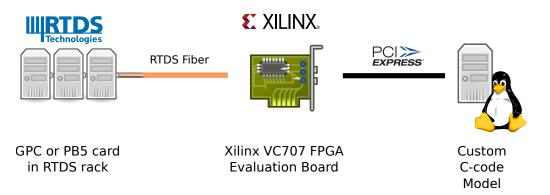

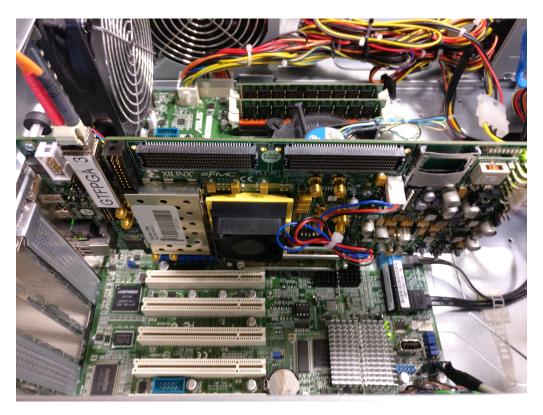

This chapter describes key components and their relationship in the *VILLASnode* and *VILLASfpga* frameworks. It starts by introducing a concept which is common to both projects. The RTDS interface is of particular importance as it is one of the main objectives for this work. The architecture is an effort to design a future-oriented framework around this interface which can be extended with other interfaces or FPGA-based models. Figure 3.1 shows a very high abstraction of the architecture. It consists of the existing RTDS simulator and a new Xilinx VC707 FPGA board which is inserted into a Intel x86\_64 computer.

## 3.1 Concept

The following concept abstracts complex co-simulation setups with can consist out of two or more subsystems. It hides slight differences in the architectures of *VIL-LASnode* and *VILLASfpga* from the user. This unified abstraction allows the integration of these frameworks. A single configuration file can be used to configure the complete setup.

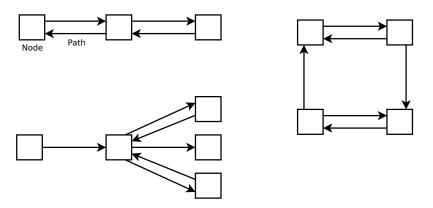

Key components in a distributed simulation are subsystems and interfaces. In the following description the terminology *nodes* and *paths* is used respectively.

A super-node is an instance of one of the frameworks (VILLASfpga or VIL-LASnode). It controls and monitors several nodes and the paths across them. Supernodes can be connected by special node-types which are called data-movers. An example for such a data-mover is a User Datagram Protocol (UDP) / IP based socket connection for the connection of two VILLASnode instances over a network

Figure 3.1: High-level Architecture of RTDS to Linux interface.

or a DMA controller for the data transfer between *VILLASfpga* and the host system which runs *VILLASnode*.

A *path* is a unidirectional pipe between *nodes*. Every path must have a single source node and can have multiple destinations. The path periodically reads samples from the source nodes and sends them to all destination nodes. Synchronization is done implicitly: A source node will block the read operation as long as there is no new data available or the processing is still underway.

A node can be a physical simulator, a HIL experiment, sensors like Phasor Measurement Units (PMUs) or virtual models. Every node is an instantiation of a specific node-type and exists in a *super-node*. Most nodes have a single input and output at which they can receive and send simulation data. Usually a node should not artificially delay the processing in addition to the time they require for solving or transmission (in case of a datamover). Hence, multiple nodes can be chained together while still being able to process a sample of simulation data in a single time step. However, there is one exception to this rule: Node-types which are interfacing real hardware must align their processing to a time step boundary. This is required to guarantee a synchronized update and sampling of real world signals across all involved nodes.

As shown in figure 3.2, this concept enables the user to build arbitrary complex topologies for co-simulation.

Figure 3.2: Possible co-simulation topologies which can be realized.

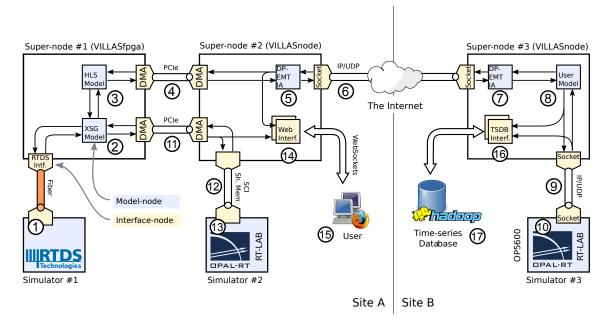

Figure 3.3 shows an example for a full-featured setup of *VILLASnode* and *VIL-LASfpga* consisting of three super-nodes and three simulators.

There are six main data paths in this example:

- 1. Simulator  $\#1 \leftrightarrow$  Simulator #2 via (1), (11) (13)

- 2. Simulator #1  $\leftrightarrow$  Simulator #3 via (1) (10)

- 3. Simulator #1 →Time-series Database (TSDB) (Hadoop) via ① ③, ① (17)

- 4. Simulator  $\#3 \rightarrow$  Time-series Database (TSDB) (Hadoop) via (10, (9, (16), (17)))

- 5. Simulator  $\#1 \rightarrow \text{User Interface (WebSockets) via } (1, 2, 1), (14, 15)$

- 6. Simulator  $\#3 \rightarrow \text{User Interface (WebSockets) via (10 (5, (14), (15)))}$

Those paths are made up of several user-defined HLS / XSG and SW-based models: (2), (3), (5) (7) and (8). In this example, the internet link between super-nodes #1 and #2 (6) is coupled in phasor domain. Nodes (5) and (7) are models which handle the transformation between DP- and EMT-domain.

Figure 3.3: Example of integrated setup consisting of two *VILLASnode* super-nodes and a *VILLASfpga* instance.

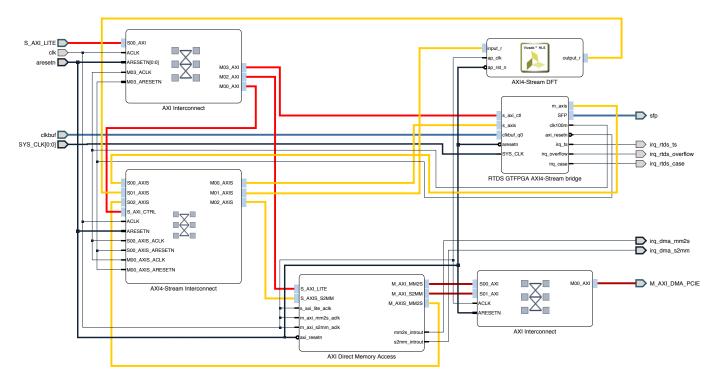

## 3.2 VILLASfpga

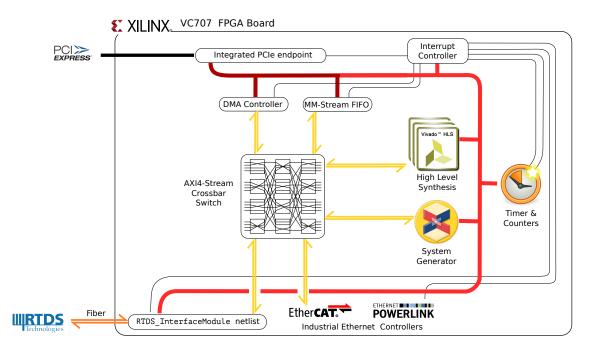

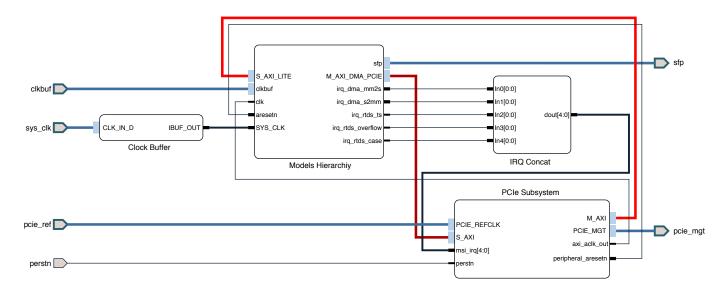

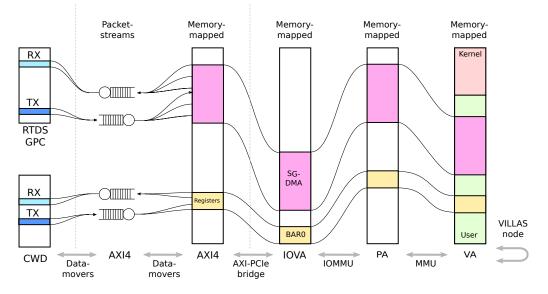

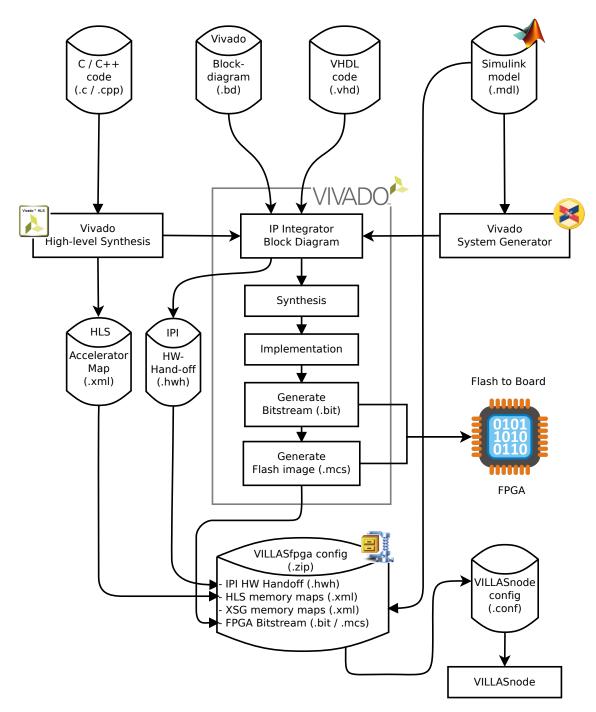

In the *VILLASfpga* framework, nodes are realized by IP blocks which are instantiated in the user FPGA-design. The type of nodes which are available for the *VILLASfpga* differ from the ones which are available for *VILLASnode*. Figure 3.4 shows the high level architecture. In this thesis, node-types for HLS and XSG models and the RTDS interface have been implemented. The concept of a path are realized by a FPGA-internal switching network which is based on AXI4-Stream busses (yellow).

Figure 3.4: The VILLASfpga architecture.

## 3.2.1 FPGA Evaluation Board

VILLASfpga is based on a VC707 evaluation board from Xilinx. The board is interfaced via PCIe to a host machine which itself runs VILLASnode and used for monitoring and controlling the VILLASfpga framework. This selection was made based on the availability of boards which are supported by RTDS for its GTFPGA interface. RTDS is selling the VC707 board as part of their MMC Support Unit<sup>1</sup>. There are also versions of the interface which are compatible with older Virtex 5 and 6 FPGAs (ML507 and ML605 boards). However only the newest 7-series FPGA families are supported by Xilinx' new Vivado development environment which will be extensively used due to its support for AXI4-based interconnect networks. Furthermore, the old FPGAs are only supported by the older Xilinx Integrated Synthesis Environment (ISE) development environment which is discontinued.

### 3.2.2 Interconnect

Figure 3.4 shows several internal and external interconnect networks used by the FPGA framework.

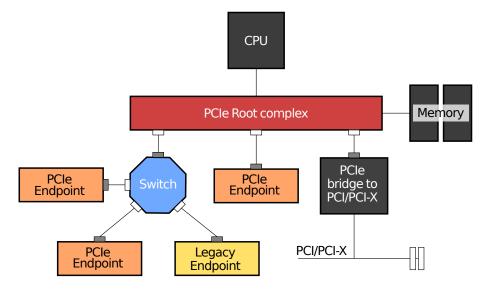

**PCIe** (black) is used for interfacing the FPGA design to the host system. It allows direct memory access from CPU to FPGA and vice versa. PCIe is a memory addressable bus. Every read and write transaction is targeting a specific address or address range. In the FPGA, the PCIe endpoint is implemented by a

<sup>&</sup>lt;sup>1</sup>https://www.rtds.com/the-simulator/our-hardware/mmc-support-unit/

hard-macro which is implemented in dedicated silicon instead of using generic FPGA resources. On the host system, the PCIe root-complex is part of the CPU or the IO Controller Hub (ICH).

- **AXI4** (dark red) is a memory-mapped bus as well. It is used only internally by the FPGA. All PCIe transactions are translated to AXI4 transactions. Only high bandwidth data-movers are connected to this bus.

- **AXI4-Lite** (red) is a simplified version of the AXI4 interconnect without the support for burst transfers. It is primarily used for register access if only single-beat transfers are required. An example for such a register access is the configuration of an IP block like the DMA controller or the change of parameters of a *node*.

- **AXI4-Stream** (yellow) is used for streaming packets between the *nodes* in the *VIL-LASfpga* framework. Unlike the memory-mapped busses, transactions are not targeting an address. They consist of one or many data-beats which are grouped to packets.

The Advanced eXtensible Interface Bus (AXI) busses are standardized by the Advanced Microcontroller Bus Architecture (AMBA) specification [1]. AMBA is a standard introduced by ARM in 1996 which defines a family of busses: Advanced High-performance Bus (AHB), Advanced Peripheral Bus (APB), AXI, AXI Coherency Extensions (ACE). Most ARM-based systems nowadays are premised on the latest generation of AXI4 interconnect.

Because of its wide-spread adoption as an industry standard, AXI4 busses have been chosen for the implementation. AXI4 busses meet all the requirements for the transfer of small packets in this application. In most use-cases they reach 100 % of the theoretical peak bandwidth.

Other protocols like IBM's Processor Local Bus (PLB) or OpenCore's Wishbone<sup>2</sup> bus have been considered as well. The decision for AMBA busses has been made due to the good availability of AXI-compatible IP by Xilinx's new Vivado Integrated Development Environment (IDE). Xilinx provides AXI infrastructure IP like interconnects, DMA controllers, clock or data width conversion free of charge.

Some of Xilinx's earlier FPGA families included hard-macro processors based on the PowerPC architecture. PowerPC is an architecture by International Business Machines Corporation (IBM) and uses the PLB as its main interconnect. Beginning with the 7-series family, Xilinx made a transition to ARM processors for their newer SoCs (Zynq). This change was accompanied with the migration from PLB to AMBA busses and the introduction of the Vivado IDE. Vivado is the successor of Xilinx's ISE and Xilinx Embedded Development Kit (EDK).

Other bus openly specified bus systems like the Wishbone bus have not been an option due to their limited support and compatibility with the Vivado IDE.

<sup>&</sup>lt;sup>2</sup>http://opencores.org/opencores,wishbone

AXI and PCIe are not buses in the traditional sense as they do not use a shared medium between all connected devices. Modern interconnection networks, also called Network-on-Chip (NoC), are only using individual point-to-point links between devices and interconnect switches. Transactions on these links are always initiated by a single master and targeting a single slave. This applies to both the memory mapped AXI4 bus, as well as the AXI4-Streaming bus. Multiple IP blocks can be linked by dedicated interconnect IP.

#### AXI4-Stream

Streaming busses have an important role in the *VILLASfpga* framework. Thus, they will be covered here in detail.

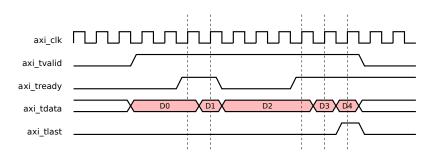

- An AXI4-Stream interface consists of usually five signals:

- **axi\_clk** is the interface clock. All other signals are synchronous to this clock meaning that they are sampled at a rising edge of this clock.

- **axi\_tvalid** is asserted by the master in the same clock cycles as data signal **axi\_tdata** holds a valid value.

- axi\_tready is asserted by the slave as soon as it is ready to accept data. A data

beat is transferred as soon as both the axi\_tvalid and axi\_tready are simultaneously asserted. axi\_tready might depend on axi\_tvalid but not the

other way around.

- **axi\_tdata** is driven by the master and contains the data beats. Xilinx requires this signal to have a width which is a multiple of 8 bit. In *VILLASfpga*ăall data signals are 32 bit IEEE-754 single precision floating point numbers.

Figure 3.5 shows a transfer of a single packet on an AXI4-Stream link. AXI interfaces are using a two-way handshake between the master and the slave. A transaction is initiated by the master by driving the first data word to axi\_tdata and asserting axi\_tvalid. The transfer of this first beat is completed by the slave as soon as it asserts axi\_tready. This allows the slave to throttle the data-transfer by de-asserting axi\_tready even during the transmission of a packet. If there is no backpressure from the slave, AXI streaming links can transfer a single data beat per clock cycle. *VILLASfpga* is using a data width of 32 bit for the axi\_tdata signal and a bus axi\_clk of 125 MHz. This results in a bandwidth of around 475 MiB s<sup>-1</sup> for the node-to-node links.

The big advantage of the streaming links is their low latency and minimal resource usage. This is a requisite for Audio / Video (AV), network and simulation applications like *VILLASfpga*. In constrast to the memory-mapped AXI4 busses there are no additional clock cycles required for the addressing.

Figure 3.5: An AXI4-Stream transaction with four data beats.

In the scope of the *VILLASfpga* framework, every time step a sample is transferred as a single AXI4-Stream packet. Multiple signals in a sample are transferred as individual data beats of this packet.

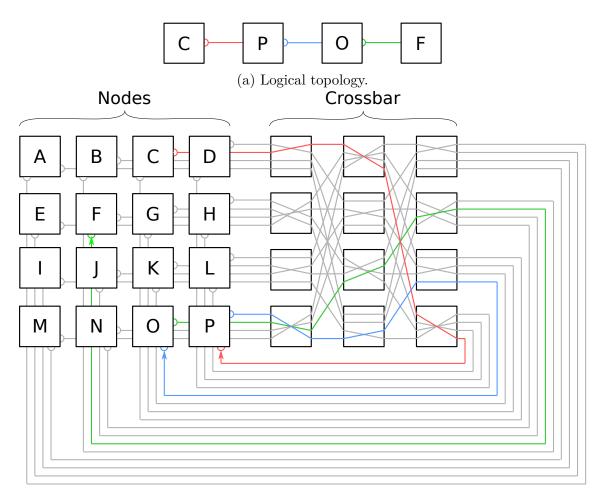

The connection of multiple *nodes* can be realized with a crossbar switch. The usage of a crossbar switch is optional but has the big advantage that routing between all connected nodes can be reconfigured during run-time. This gives the user the ability to test multiple different variants of a certain model or quickly switch between multiple configurations without resynthesizing the FPGA bitstream. Figure 3.6 shows 16 *nodes* which are connected to a crossbar. In the example, the crossbar is configured to route packets from source node C over hops P and O to the destination F. Figure 3.6a shows a logical abstraction of the same configuration. Xilinx's AXI4-Stream interconnect IP core supports up to 16 master and slave interfaces.

#### 3.2.3 Data-movers

As stated earlier, *VILLASfpga* is using PCIe as its interface to the host machine. Because this is a memory mapped bus, special node-types, the data-movers, are required which translate the memory-mapped data on the AXI and PCIe busses to packets on the AXI4-Stream links. Chapter 2.7.1 introduced two different approaches for data transfer between the FPGA and the CPU. To compare their performance, three different data-movers have been tested: Both a simple and a SG DMA controller as well as a First-in First-out (FIFO) queue which is controller via PIO. Every datamover is realized as a node-type as part of the VILLAS concept.

VILLASfpga is not limited to a single instance of those data-movers. If desired, the user has the choice which and how many data-movers will be instantiated in the design. However, for most use cases a single data mover is sufficient.

#### 3.2.4 Models

FPGA-based models profit from clock cycles as low as 5 ns and nearly unlimited parallelism offered by the nature of Programmable Logic (PL) devices. Often used in Rapid Control Prototyping (RCP) and simulation of power electronic converters, these models use very small time step periods. For such applications, a model which

#### $3 \ Architecture$

Figure 3.6: Connectivity options of a 16-by-16 AXI4-Stream switch crossbar.

has been previously simulated in *VILLASnode* or another simulator can be moved to the FPGA. In this case, the PCIe interface would no longer be used for data exchange but only to monitor and control the FPGA models.

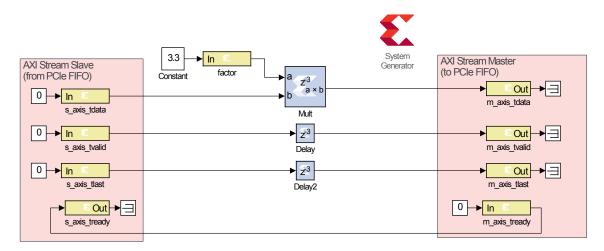

To exploit the full capabilities of FPGAs, custom Hardware Description Language (HDL) code like VHSIC Hardware Description Language (VHDL) or Verilog has to be written. However, implementing bigger models using HDL is cumbersome and error prone. Instead, more user-friendly and graphical RCP tools like Mathwork's Simulink, or National Instrument's LabVIEW are used. This ongoing trend in digital design raises the level of abstraction and is often referred to as Electronic System-level Design (ESL) design. It hides details of the Register Transfer Level (RTL) from the designer and enables them to focus on the design and behaviour of their model. Yet, the designer has still to keep in mind the underlying FPGA architecture to obtain an efficient implementation. A critical decision is the selection of a suitable number format to discretize continuous quantities. Xilinx is providing their own optimized Simulink blockset called Vivado System Generator for DSP (XSG) which assists the designer in those considerations.

Alternatively, Mathworks offers a product called Simulink HDL coder. It can transform any Simulink model consisting of standard blocks into HDL code. This simplifies the adoption existing models to a FPGA implementation. Though, the results of Simulink HDL coder are not optimized for a specific FPGA architecture. In fact, the generated HDL code is generic and could be implemented on most FPGAs or even in hard silicon.

Vivado High-level Synthesis (HLS) is another method introduced by ESL design. It uses high-level programming languages as design entry. With certain restrictions, HLS tools will transform this high-level language into HDL code. Xilinx supports both C and C++ languages in its HLS tool. HLS is a very young technology. Xilinx released the first version of HLS in 2013. Major improvements can be seen with every released version of the tools.

In the course of the *VILLASfpga* implementation, both simple HLS and XSG models have been implemented to provide a starting point for more complex models designs in the future.

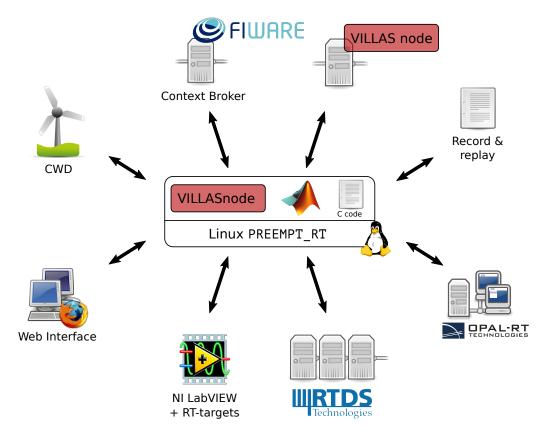

# 3.3 VILLASnode

VILLASnode implements the previously described concept as a software application which runs on a Linux machine. Figure 3.7 shows several of the currently supported node-types. Until now, VILLASnode has been mainly used as a gateway. However, simple models can be implemented as a custom node-type using C code. In addition VILLASnode is also used to control the VILLASfpga PCIe card which are plugged into the same system. In this case, every datamover between VILLASfpga and VILLASnode appears as a node in both frameworks. For the best performance VILLASnode has been written in the C programming language and optimized for

#### 3 Architecture

Figure 3.7: Overview of supported node-types by VILLASnode.

real-time operation. So for example, every path is processed in a dedicated thread to guarantee a non-blocking operation.

As a little addition to the previously described concept, *VILLASnode* supports hook functions which can be assigned to paths. These hook functions are executed for every sample of simulation data. They can be used to alter the signals, e.g. applying a simple filter operation, or filter the data based on various criteria. Most of the node-types for example can not handle simulation time steps as low as 50 µs. Instead a hook function is employed to reduce the interface rate. Other use cases of hook functions are the collection of statistics, monitoring of the link qualities the implementation of interface algorithms.

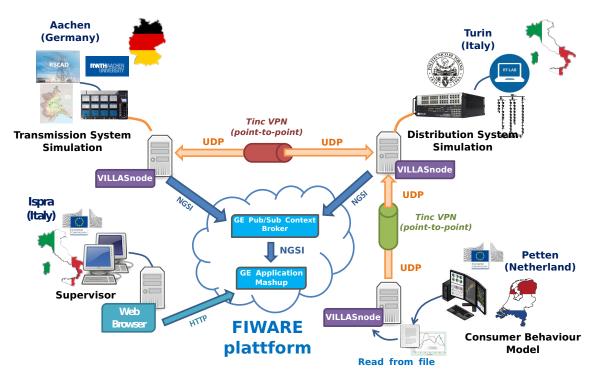

Figure 3.8 shows an example setup for internet-distributed simulation. Here every site runs a dedicated *VILLASnode* instance. Locally available simulators are connected to their corresponding *VILLASnode* instances. Communication between the sites is handled by *VILLASnode* which is acting as a gateway.

Figure 3.8: European Real-time Integrated Co-simulation laboratory (ERIC-LAB) demonstration.

# 3.4 Host Machine

The host machine's main task is to run the *VILLASnode* software and to house the *VILLASfpga* PCIe-card. To have plenty of margin for models being executed in the *VILLASnode* framework, a recent Intel x86\_64 multi-core system was chosen. A multi-core machine allows the concurrent execution of multiple paths / models on different cores. The only alternative with approximate performance are ARM-based systems. However, they rarely feature full-sized PCIe slots which are required for the VC707 FPGA-board.

Instead of a dedicated FPGA-board, an integrated FPGA-CPU System-on-Chip (SoC) like Xilinx's Zynq architecture could be selected. It combines a PL with two ARM processor cores (PS). Both parts of the architecture are tightly interconnected by a total of nine AXI busses. It would provide the best connection between *VILLASnode* which would run on the ARM cores and *VILLASfpga* which would be implemented in the PL. Unfortunately, this FPGA architecture is not officially supported by RTDS for its GTFPGA interface. Even though there are Zynq-based SoC's which are using the same Virtex-7 architecture for their programmable logic as the VC707 board, it is questionable whether the RTDS interface would work. Most parts of the *VILLASfpga* architecture are designed with the adaptability to Zynq SoC's in mind. For deployments where power consumption or size are critical, both *VILLASnode* and *VILLASfpga* could be ported to a Zynq-based system without larger changes. The host machine runs a Fedora Linux OS for the execution of *VILLASnode*. Linux is not a real-time OS by default. Hence, careful optimizations and tuning are indispensable. The most important change is a PREEMPT\_RT-patched kernel. PREEMPT\_RT<sup>3</sup> is patch-set maintained by Thomas Gleixner to improve the real-time performance of the vanilla<sup>4</sup> Linux kernel.

The VILLASnode code and its portion which controls VILLASfpga is running in the Linux userspace. Device drivers are usually part of the OS and therefore run in kernelspace. However, this would cause a big number context switches between the userspace application and the kernelspace driver. To eliminate this overhead the driver was implemented as part of the userspace application. Yet, the driver still needs to request resources from the OS: FPGA device memory needs to be mapped into the userspace application and interrupts have to be forwarded. Linux is providing two APIs which enable the implementation of PCIe device drivers in userspace. By using one of those standard APIs an unmodified Linux kernel can be used. This simplifies the maintenance and setup of the host machine. Both the UIO and VFIO APIs have been considered and are presented in the following sections.

## 3.4.1 Userspace IO (UIO)

UIO is Linux' first API for device drivers in userspace. It was introduced to Linux in 2007 with version  $2.6.23^5$ .

The UIO framework allows that certain parts of the driver can still remain in kernel while most of it is implemented in userspace. The kernel stub part of the UIO driver exposes its capabilities via ioctl() and mmap() system calls to the userspace.

For most Peripheral Component Interconnect (PCI) devices the generic uio\_pci\_generic kernel module can be used. It exposes access to the PCI BAR via mmap() and allows the passthrough of legacy PCI interrupts.

A major limitation of UIO is the fact that PCI devices are not allowed to act as a bus master. Bus mastering describes the ability of a PCI device to initiate transactions on the bus. Acting as a master allows the device to access host memory or other PCI devices directly. This is considered dangerous if not controlled by the operating system itself and therefore disabled by UIO.

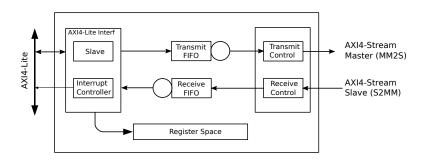

Without the ability to access host memory, DMA transfers are impossible. MSI interrupts rely on bus mastering as well and are therefore disabled. Without PCIe Message Signalled Interrupt (MSI) only the legacy interrupt mechanism is available which does not support vectors. To multiplex different interrupt sources an additional interrupt controller is then required.

<sup>&</sup>lt;sup>3</sup>https://www.osadl.org/Realtime-Linux.projects-realtime-linux.0.html

<sup>&</sup>lt;sup>4</sup>A vanilla kernel is the unmodified upstream version of the Linux kernel.

<sup>&</sup>lt;sup>5</sup>http://git.kernel.org/git/?p=linux/kernel/git/torvalds/linux-2.6.git;a=commit; h=beafc54c4e2fba24e1ca45cdb7f79d9aa83e3db1

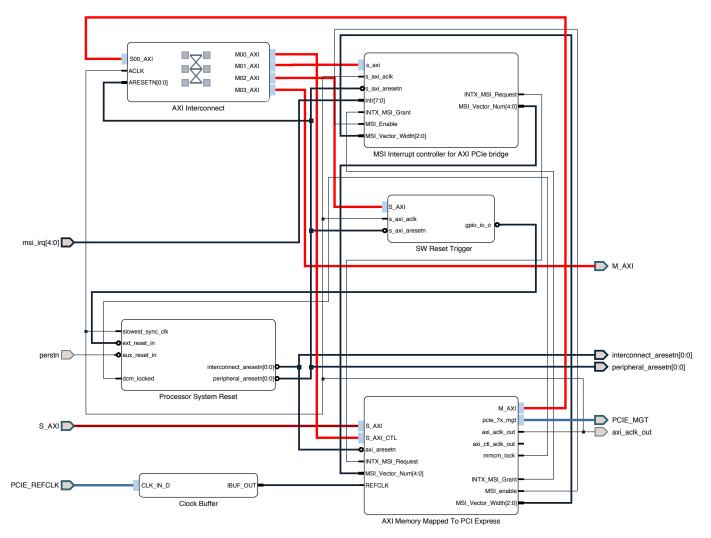

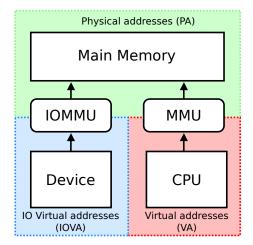

## 3.4.2 Virtual Function IO (VFIO)

VFIO is a newer API for accessing devices directly from userspace. It was introduced to Linux in 2012 with version  $3.6^{-6}$ .

It has been primarily designed to improve the performance of PCI devices in Kernel-based Virtual Machine (KVM). KVM is a full virtualization solution for Linux which runs Virtual Machines (VMs) as a userspace processes. VFIO provides a secure way to assign a PCIe device to a VM. To enhance the performance of those PCIe devices they must be able to utilize their DMA controllers which in turn requires that the PCIe devices must have bus mastering capabilities. Though, as stated earlier, bus mastering can be dangerous as the PCIe device gains full control over the system. In case the PCIe device is assigned to a VM or an userspace application, an attacker who controls either one of those can gain access to the host system. With the introduction of Intel's VT-d virtualization technology, Input / Output MMUs (IOMMUs) and PCIe root complexes gained the flexibility to effectively isolate PCIe devices from each other and the host memory. By isolation, the device can be limited to access only certain parts of the address-space which belong to the controlling userspace process. Thus the PCIe device is prohibited to cause harm by accesses to the host kernel memory or other VMs.

Furthermore, VFIO provides a comprehensive ioctl()-based API to create DMA memory mappings, register MSI interrupts and more. DMA mappings and BAR accesses are created by using the mmap() system call. While UIO always requires root permissions, VFIO can make use of Linux permissions system to allow arbitrary users access to the PCIe device. This could be advantageous in environments like HPC clusters where root access is restricted.

# 3.5 Real-time Digital Simulator (RTDS)

To demonstrate the functionality and performance of *VILLASfpga*, an interface to the RTDS has been implemented. This interface can be seen as an example for the extensibility of the *VILLASfpga* framework. As it is described below, RTDS is based on custom hardware which also holds for the simulation software environment. As such, it is a perfect example of mitigating interface issues of a vendor specific solution based on a generic framework proposed in this thesis.

This sections starts by presenting the architecture of the Real-time Digital Simulator (RTDS). RTDS is one of the two big players for digital real-time power system simulation. With its introduction in 1993 RTDS was one of the first commercial fully DRTS on the market [14].

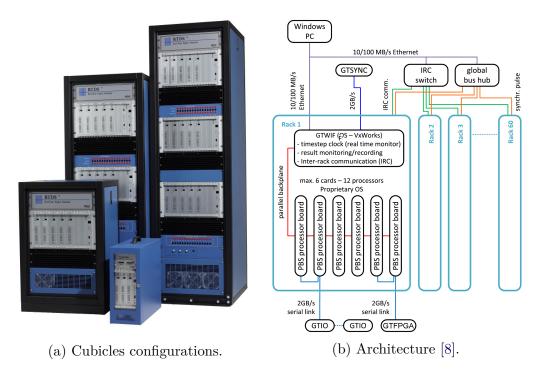

Figure 3.9a shows a typical setup of a RTDS simulator which can be built up of one or more cubicles. Each cubicle houses one or more racks. Each rack can be used

<sup>&</sup>lt;sup>6</sup>https://git.kernel.org/cgit/linux/kernel/git/torvalds/linux.git/commit/?id= cba3345cc494ad286ca8823f44b2c16cae496679

#### 3 Architecture

Figure 3.9: The Real-time Digital Simulator.

standalone or in combination with others for the simulation of larger systems. In case of a multi-rack simulation an IRC is used to exchange simulation data and a Global Bus Hub (GBH) is used to synchronize the time step between racks.

Each rack can contain up to six processing cards which are interconnected by a backplane. Processing cards are the core of each simulator. They compute control signals and the power system solution. RTDS is therefore continually updating its processing cards. Table 3.1 gives an overview of existing generations of RTDS processor cards.

A Giga Tranceiver Workstation Interface card (GTWIF) controls the time step of a rack and coordinates communication over the rack backplane. It also handles inter-rack communication and controls the rack by an Ethernet connection from a RSCAD workstation.

Figure 3.9b shows the architecture of RTDS.

|      |       |                        |          | 1                        |                   |

|------|-------|------------------------|----------|--------------------------|-------------------|

| Year | Abbr. | Name                   | $\#^{7}$ | Processor                | Speed             |

| 1993 | TPC   | Tandem Processor card  | 2        | Analog Devices ADSP21062 | $12\mathrm{MHz}$  |

| 1997 | 3PC   | Tripple Processor card | 3        | Analog Devices ADSP21062 | $40\mathrm{MHz}$  |

| 2002 | RPC   | RISC Processor card    | 2        | IBM PowerPC 750CXe       | $600\mathrm{MHz}$ |

| 2005 | GPC   | Giga Processor card    | 2        | IBM PowerPC 750GX        | $1\mathrm{GHz}$   |

| 2011 | PB5   | PB5 Processor card     | 2        | Freescale MC7448         | $1.7\mathrm{GHz}$ |

Table 3.1: Generations of RTDS processor cards.

Recent processing cards support the attachment of peripherals via *Giga Tranceiver (GT)* fiber optic connections. Commonly found extensions modules are Giga Tranceiver Input Output card (GTIO) or GTNET. A variety of different input / output cards (GTDI, GTDO, GTAI, GTAO, GTFPI) enable the attachment of HIL hardware to the simulator. The GTNET card allows data-exchange via standard protocols like IEC 61850 Sampled Values, GOOSE, UDP, Transmission Control Protocol (TCP) and more.

The following subsections highlight extension cards which are important for the interface between RTDS and the co-simulation framework.

## 3.5.1 Giga Tranceiver Network card (GTNET)

The GTNET extension card provides a real time communication link to and from the simulator via Ethernet. Several industry standard protocols like IEC 61850-9-2 SV, GOOSE, Distributed Network Protocol (DNP3) or custom UDP / TCP protocols are supported via exchangeable firmwares. The latest version of the GTNETx2 card consists of two GTNET modules. Every module can execute a certain firmware which enables simultaneous operation of two different protocols. Other features include record and playback of large datasets from the workstation machine. The card offers 100/1000 Copper, 100BASE-FX, or 1000BASE-SX fiber connections for the interface to Ethernet networks.

At first glance this makes the GTNET card a perfect candidate for interfacing RTDS to other simulators. Unfortunately, it is impossible to synchronize the interfaces to the internal time step which is a premise for a tight coupling of two simulators. The next section introduces an alternatives interface which supports synchronization.

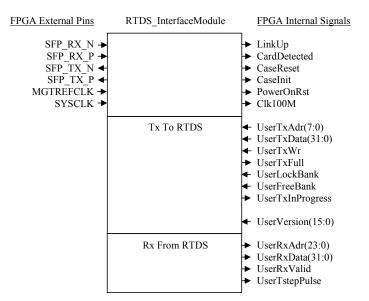

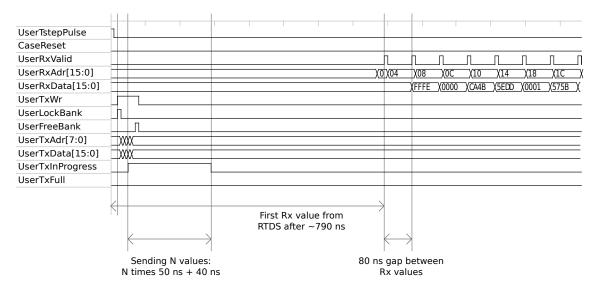

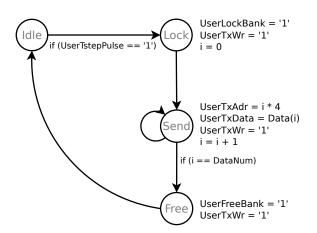

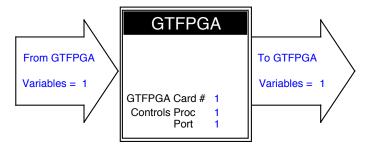

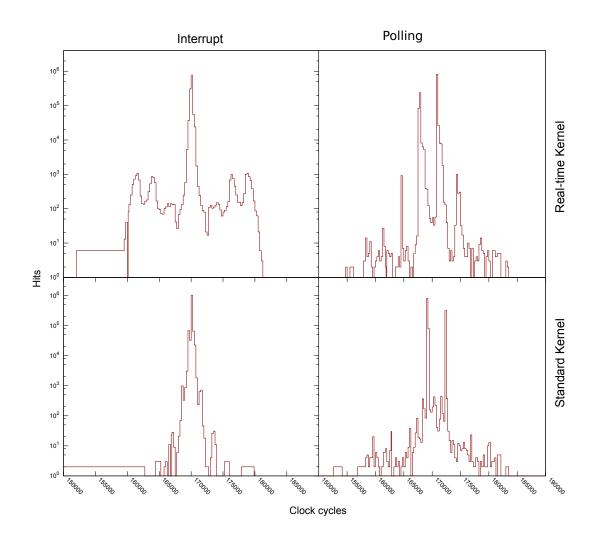

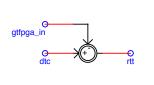

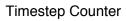

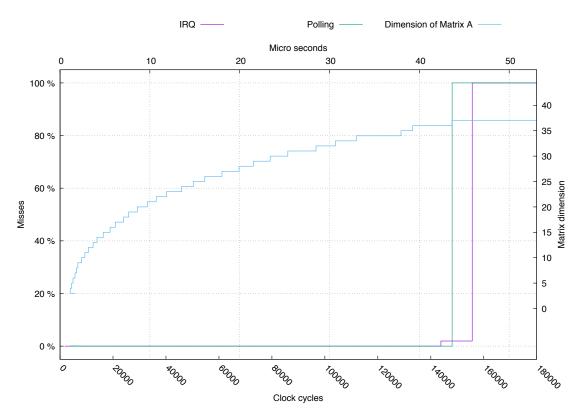

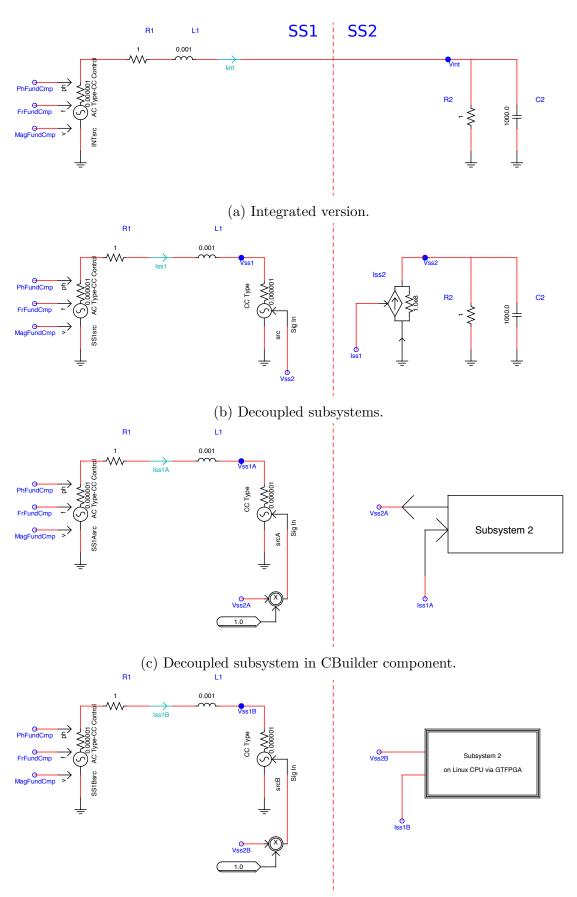

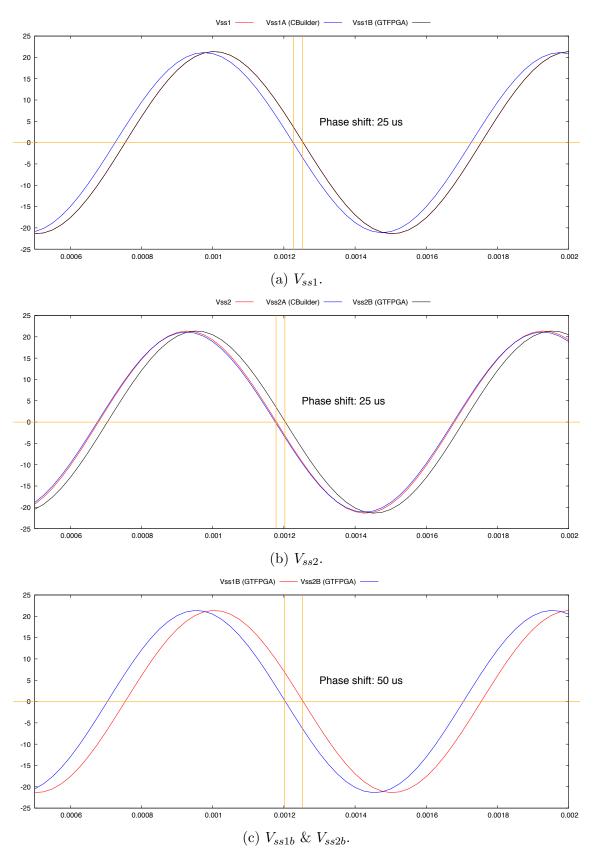

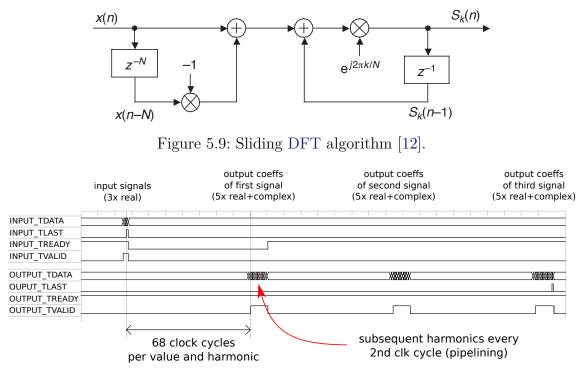

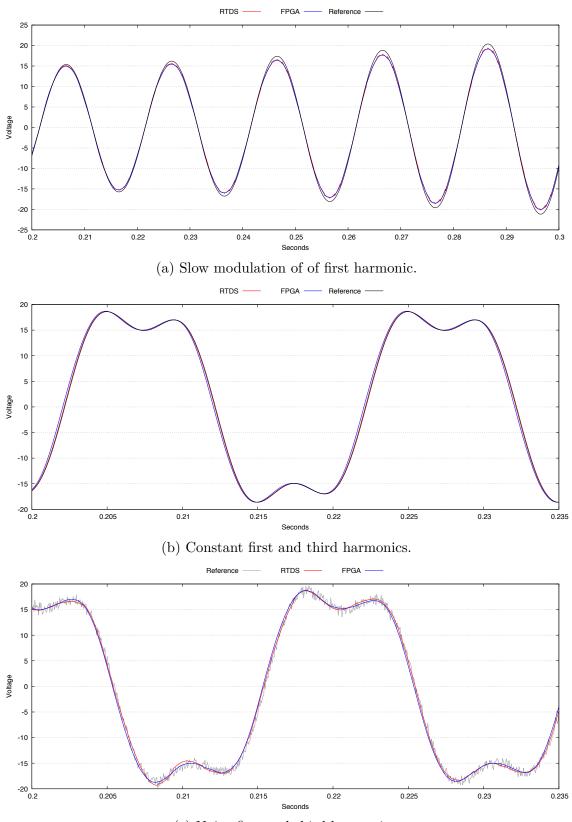

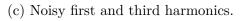

# 3.5.2 Giga Tranceiver Field Programmable Gate Array (GTFPGA)